1. 2次元トンネルFET

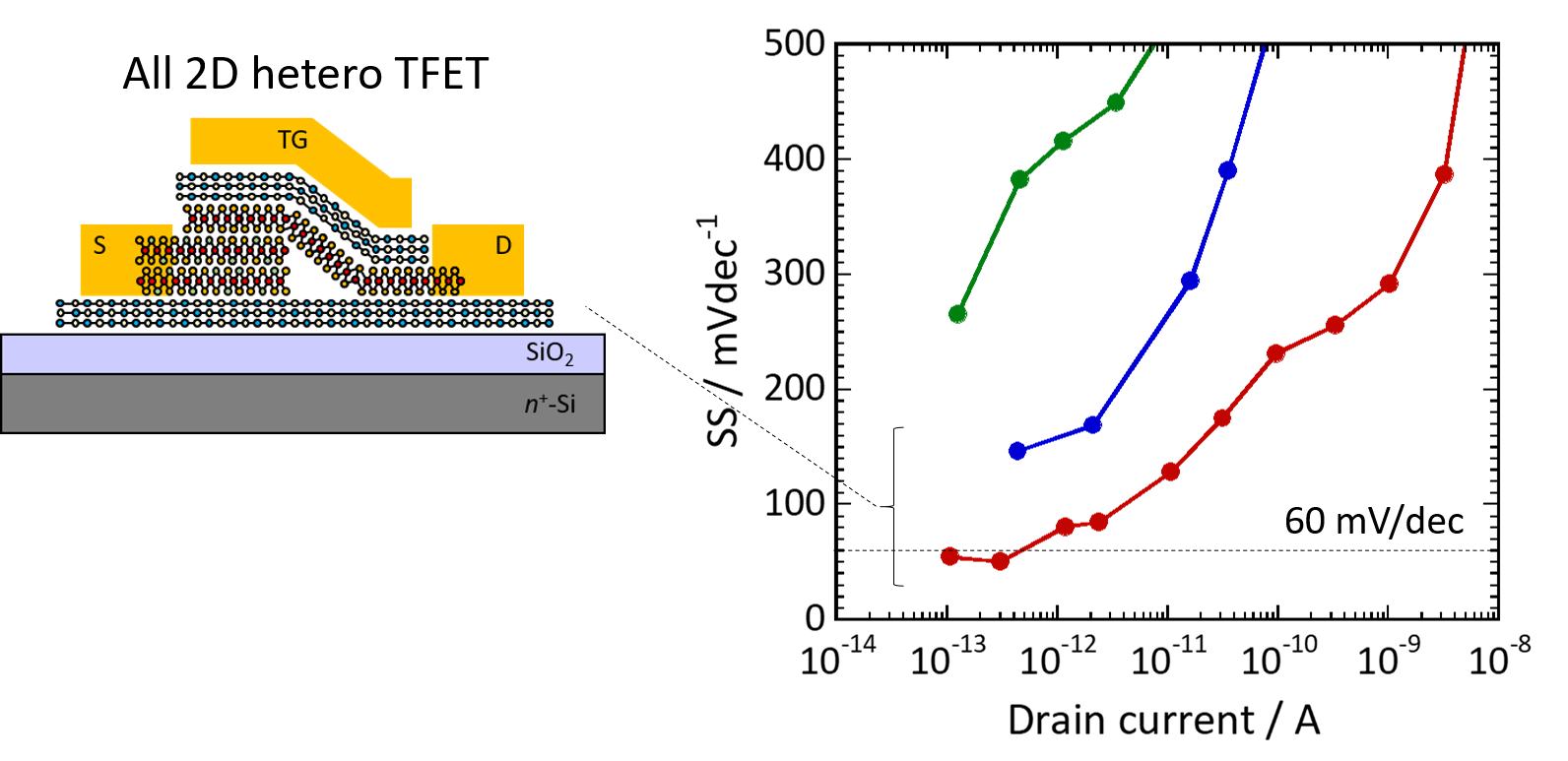

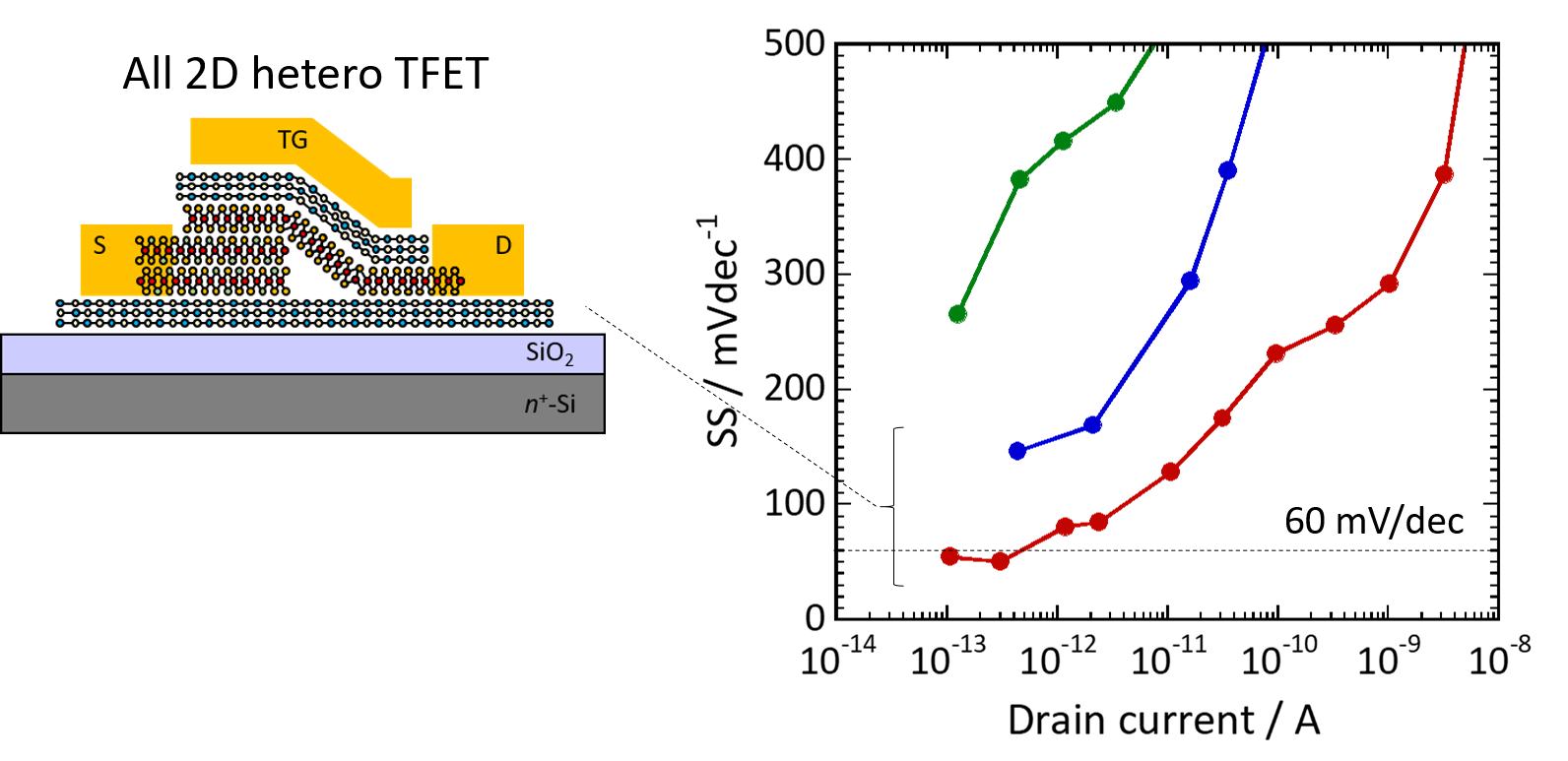

低消費電力化につながるサブスレッショルド電圧の低減のためトンネルFETが注目を集めていますが、トンネル現象ゆえオン電流が小さいという欠点があります。理想的にはvad der Waals距離にまでトンネル距離を低減できる2次元層状へテロ構造を利用したトンネルFETを研究しています。[埼玉大上野G, NIMS谷口・渡邊G共同研究]

▲(左)p+-MoS2/n-MoS2とh-BNを組み合わせ完全2次元トンネルFETを形成した。(右)SSのId依存性。MOSFETの理論限界であるSS=60mV/decを切る値を達成。(中村君2020.3修了)

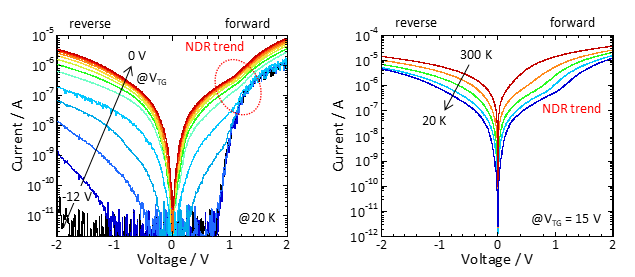

▲(左)ダイオード特性のゲートバイアス依存性からtypeIIからtypeIIIバンドアライメントへ変化していることがわかる。BTBTから拡散への変化も明確に観察される。(右)ダイオード特性の温度依存性から低温で負性微分抵抗(NDR)トレンドが観測されており、typeIIIでreverse側はバンド間トンネルであることがわかる。(中村君2020.3修了,何君2018.3修了)

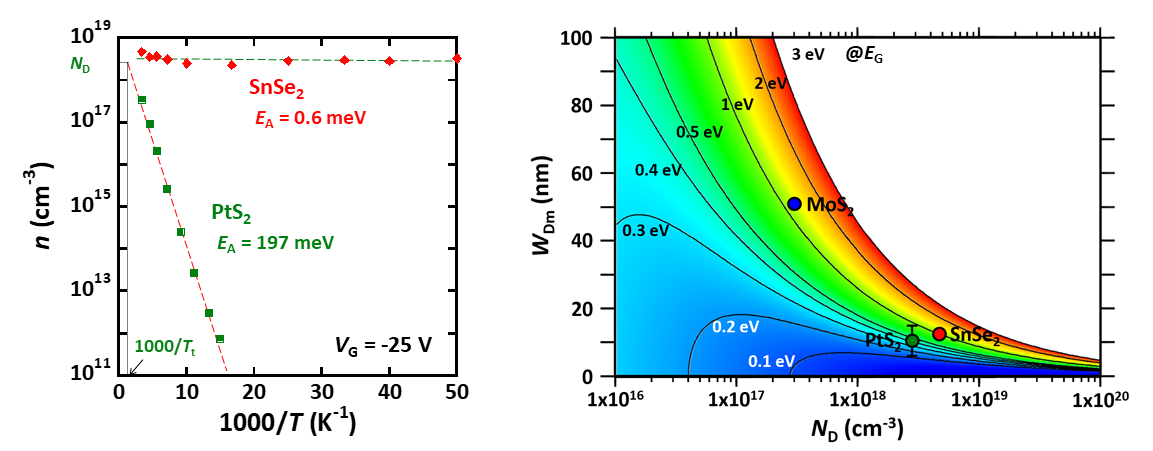

▲(左)N+結晶候補としてSnSe2とPtS2のHall計測を行った結果、SnSe2は4.7*1018 cm-3であり、PtS2は3.6*1017 cm-3であった。SnSe2の方が高濃度結晶であり、活性化エネルギーも小さく低温でもキャリアが熱励起されていることからTFETのN+ソース結晶として適している。(右)SnSe2とPtS2のId-Vgからゲート変調しなくな膜厚を最大空乏層厚さと仮定した場合、ほぼ同じであるがバンドギャップの違いでキャリア数は異なる。(佐藤君2021.3修了)

Ref.

J. He, N. Fang, K. Nakamura, K. Ueno, T. Taniguchi, K. Watanabe, and K. Nagashio, "2-Dimensional Tunnel FETs with a Stable Charge-Transfer-Type p+-WSe₂ Source", Adv. Electronic Mater. 2018, 4, 1800207.

K. Nakamura, N. Nagamura, K. Ueno, T. Taniguchi, K. Watanabe, K. Nagashio, "All 2D heterostructure Tunnel Field Effect Transistors: Impact of Band Alignment and Heterointerface Quality", ACS Applied Materials & Interfaces, 2020, 12, 51598−51606.

Y. Sato, T. Nishimura, D. Duanfei, K. Ueno, K. Shinokita, K. Matsuda and K. Nagashio, "Intrinsic Electronic Transport Properties and Carrier Densities in PtS2 and SnSe2: Exploration of n+-Source for 2D Tunnel FETs", Adv. Electronic Mater., 2021, 7, 2100292.

Hiroto Ogura, Seiya Kawasaki, Zheng Liu, Takahiko Endo, Mina Maruyama,Yanlin Gao, Yusuke Nakanishi, Hong En Lim, Kazuhiro Yanagi, Toshifumi Irisawa, Keiji Ueno, Susumu Okada, Kosuke Nagashio, Yasumitsu Miyata, "Multilayer In-Plane Heterostructures Based on Transition Metal Dichalcogenides for Advanced Electronics", ACS nano, 2023, 17, 7, 6545-6554.

2. 2D材料(MoS2等)の成長・輸送特性・容量評価

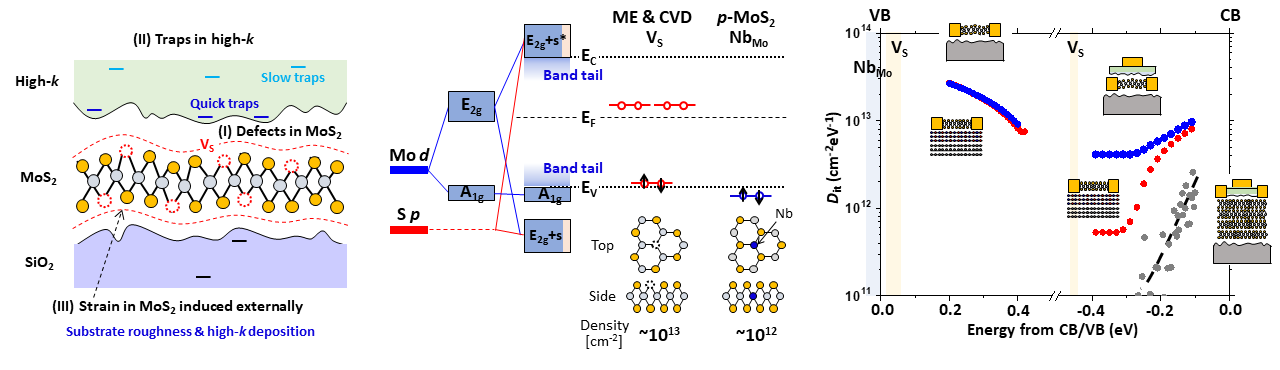

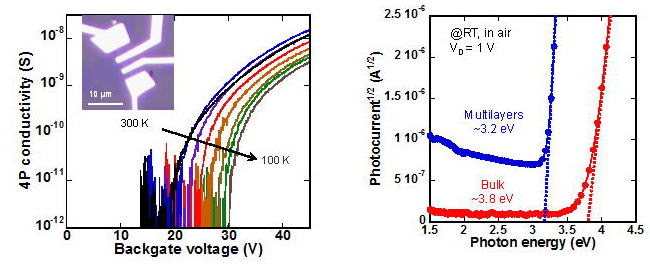

バンドギャップを有する2次元層状物質であるMoS2は、単層で直接遷移型となるため、電子デバイスとしてだけでなく、光デバイスとしても注目されています。しかしながら、結晶性の良いKishグラファイトと比較して現時点では、結晶性の良いバルク結晶は育成できておらず、S欠陥が1013cm-2程度含まれることが知られています。この欠陥がどのように輸送特性に影響を与えるかを調べています。

▲(左)high-k/MoS2/SiO2スタックにおいて形成される界面凖位の3種類の起源。(中)MoS2は配位子場でバンドが決まる。Mo原子のd起動のスプリッティングで伝導帯と価電子帯が形成される。S欠陥凖位はミッドギャップ及び価電子帯側に形成される。(左)伝導帯側は、2Dヘテロで原子レベルでフラットな界面を形成すれば、歪による凖位は低減される。一方、価電子帯側は、S欠陥凖位のため界面凖位が高くヘテロを組んでも改善されない。(方楠君&豊田君2019.3修了)

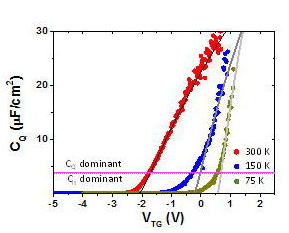

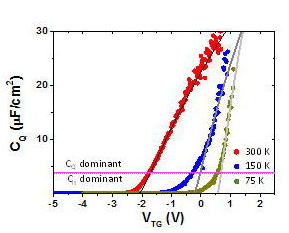

▲(左)単層MoS2の量子容量(CQ)の温度依存性。界面凖位がメインとなる低C領域よりも大きいCQ領域においては理論との良い一致を示している。原子レベルで薄いMoS2では、C-V測定はMoS2の量子容量で決定されることがわかる。(方楠君2019.3修了)応用物理学会講演奨励賞受賞2018.3

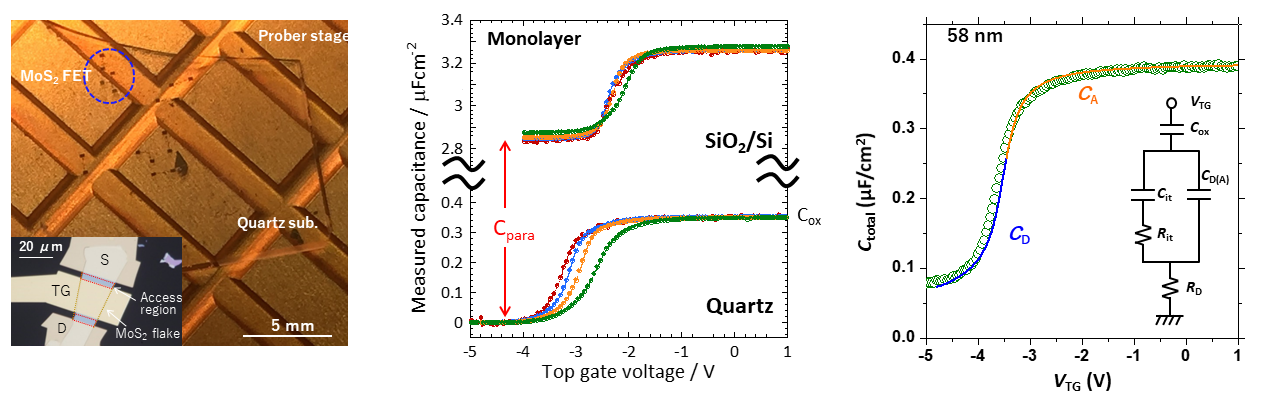

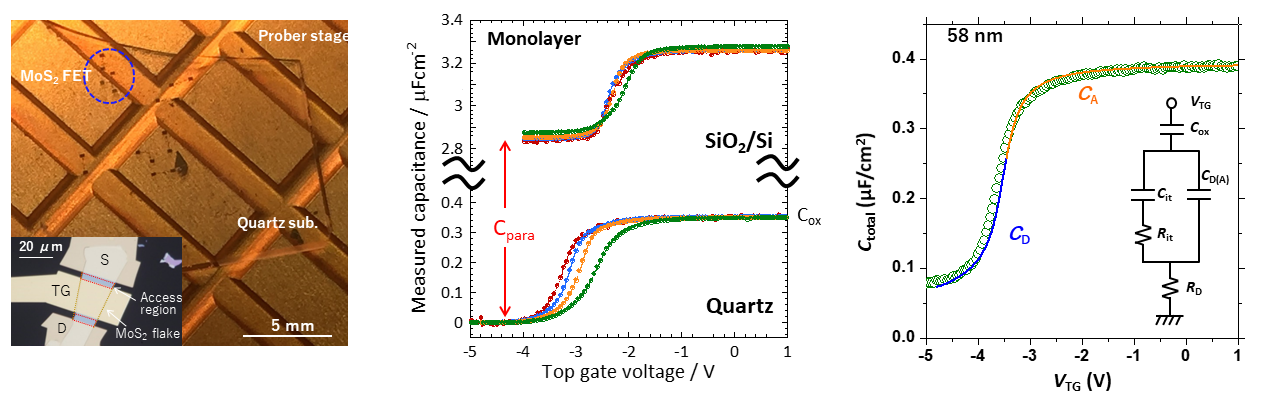

▲(左)石英上に作成したMoS2FETデバイス。(中)。Si基板上と比較して浮遊容量がほぼ消滅しており、容量計測では石英基板が必須である。(右)多層MoS2の容量計測結果。石英基板であるため、空乏側を正確に決めることができる。

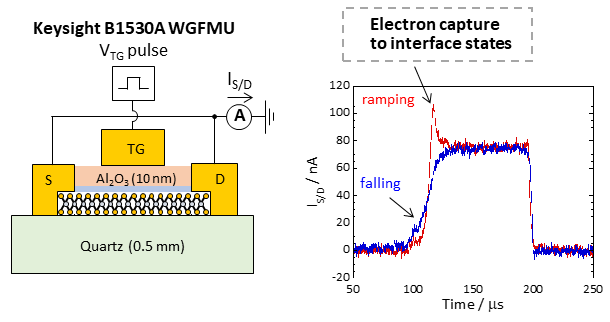

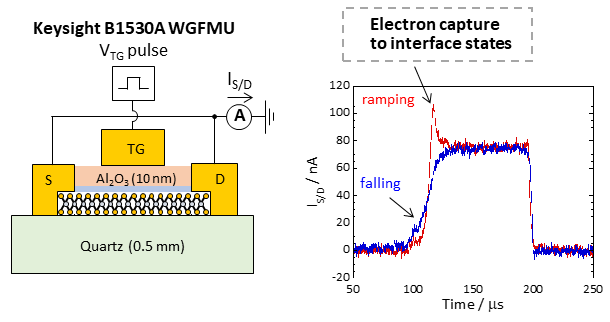

▲(左)B1530A WGFMUを用いて単層MoS2にTime domain charge pumping法を適応した。(右)界面での電子トラップとデトラップを初めて観測した。(谷口君2018.3修了)

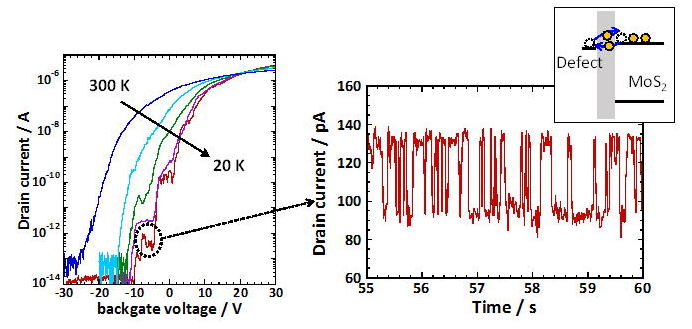

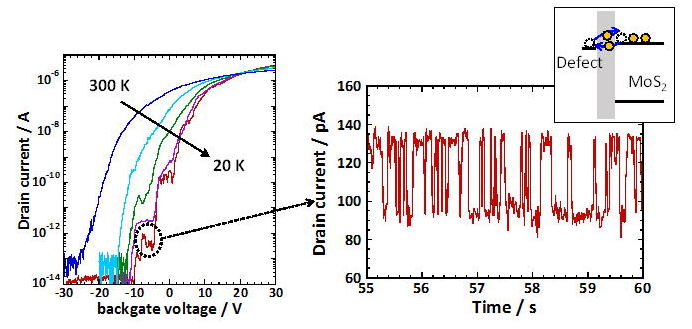

▲(左)単層MoS2 FETの温度依存性。温度の低下と共にトランスファー曲線がギザギザになる。(右)ギザギザのでるゲートバイアスで電流の時間変化を追うとランダムテレグラフノイズ(RTN)が観測される。多端子デバイス解析から電子が欠陥にトラップされる挙動を観測していることがわかった。(方楠君2019.3修了)SSDM若手奨励賞受賞2016.9

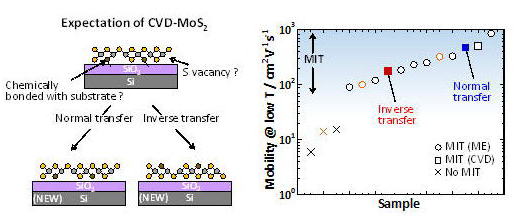

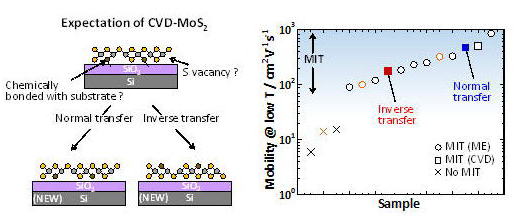

▲(左)CVD成長したMoS2の上側と下側のSのどちらが欠陥が多いかを通常転写と反転転写により輸送特性を評価した。(右)どちらも金属絶縁体遷移が観測され、他の報告と比較して高い移動度を示したことから、輸送現象からは上下の結晶性に観測できるほどの差は認められなかった。(倉林君2017.3修了)

Ref.

S. Kurabayashi, and K. Nagashio, ”Transport properties of the top and bottom surfaces in monolayer MoS2 grown by chemical vapor deposition”, Nanoscale, 2017, 9, 13264-13271.

N. Fang, K. Nagashio, and A. Toriumi, "Subthreshold transport in mono- and multilayered MoS2 FETs", Appl. Phys. Express, 2015, 8, 065203.

N. Fang, K. Nagashio, and A. Toriumi, "Experimental detection of active defects in few layers MoS2 through random telegraphic signals analysis observed in its FET characteristics", 2D mater., 2017, 4, 015035.

N. Fang, K. Nagashio, "Band tail interface states and quantum capacitance in a monolayer molybdenum disulfide field-effect-transistor", J. Phys. D, 2018, 51, 065110.

N. Fang, and K. Nagashio, "Accumulation-mode two-dimensional field-effect transistor: Operation mechanism and thickness scaling rule", ACS appl. mater. interfaces, 2018, 10, 32355.

K. Taniguchi, N. Fang, and K. Nagashio, "Direct observation of electron capture & emission processes by the time domain charge pumping measurement of MoS2 FET", Appl. Phys. Lett. 2018, 113, 133505.

W. Li, et al., "Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices", Nature Electronics, 2019, 2, 563–571.

N. Fang, S. Toyoda, T. Taniguchi, K. Watanabe, and K. Nagashio, "Full energy spectra of interface state densities for n– and p-type MoS2 field-effect transistors", Adv. Func. Mater. 2019, 29, 1904465.

N. Fang and K. Nagashio, "Quantum-mechanical effect in atomically thin MoS2 FET", 2D mater, 2020, 7, 014001.

Ryoichi Kato, Haruki Uchiyama, Tomonori Nishimura, Keiji Ueno, Takashi Taniguchi, Kenji Watanabe, Edward Chen, Kosuke Nagashio, “p-type conversion of WS2 and WSe2 by position-selective oxidation doping and its application in top gate transistors”, ACS appl. mater. interfaces, 2023, 15(22), 26977-26984.

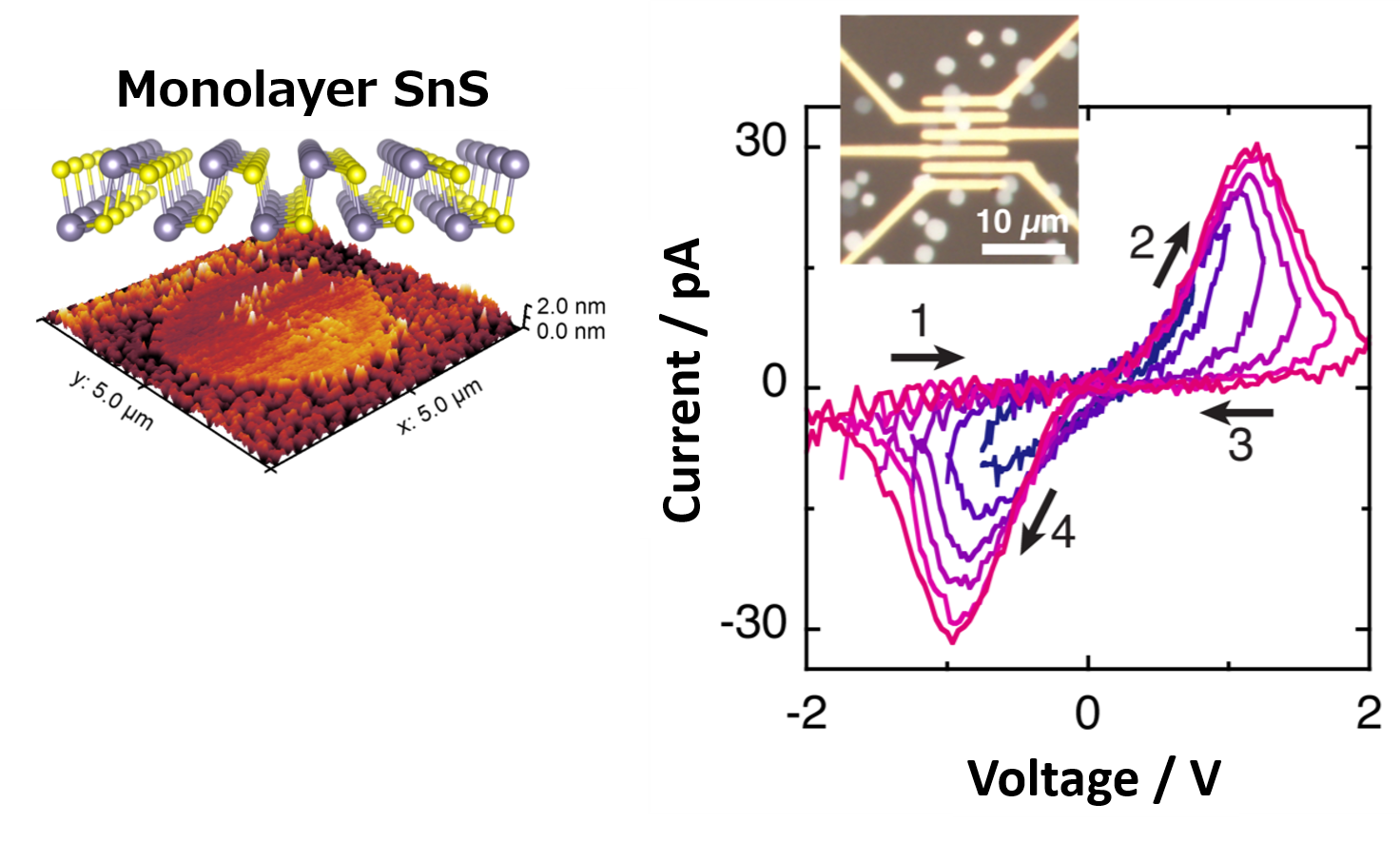

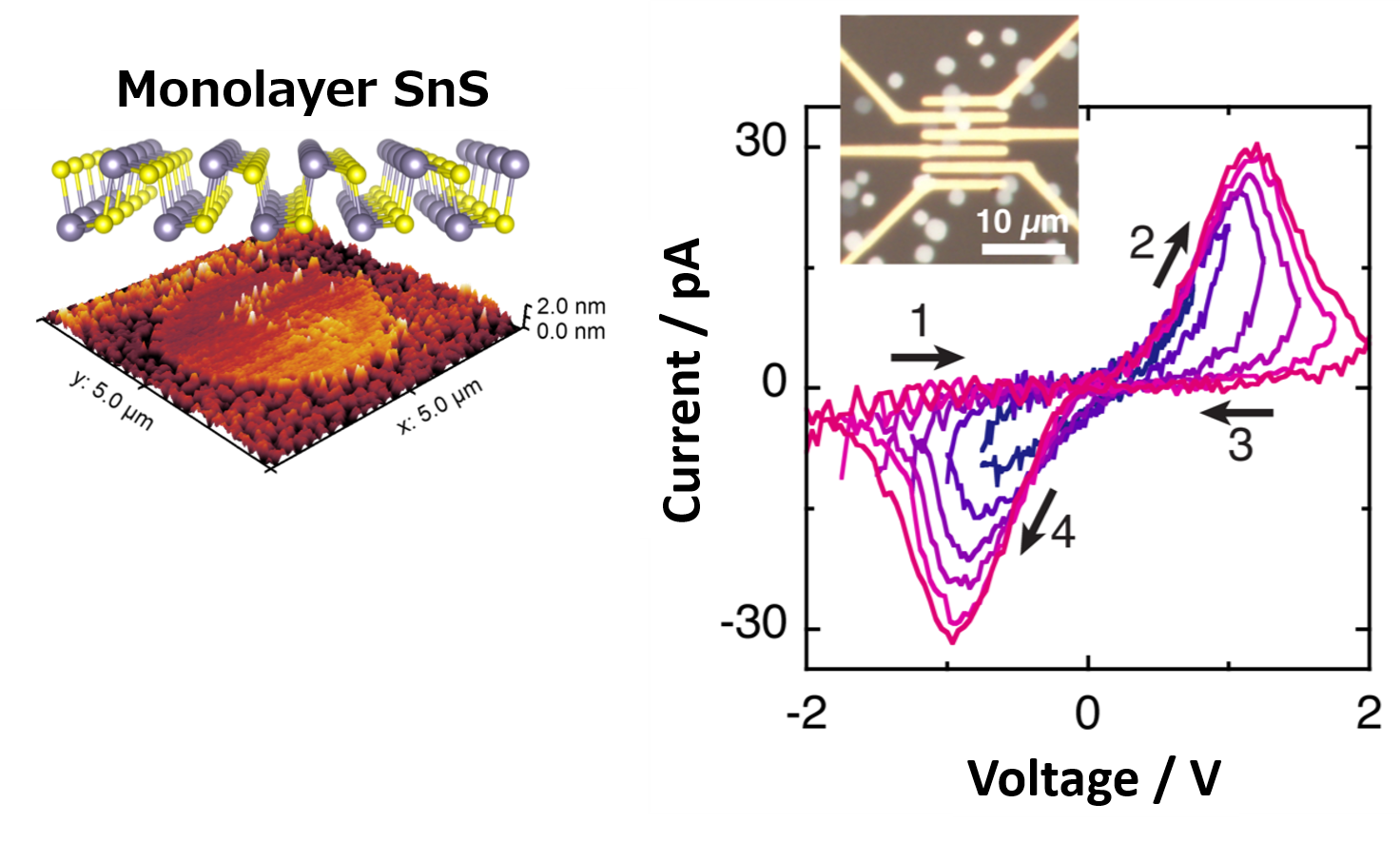

3. 環境発電を目指した圧電/強誘電2次元SnS

2次元層状物質の中には圧電特性を示すものがあり非点対称性の単層SnSはPZTと同等の圧電定数dを有することが理論的に予測されている。層間力はvdWだけでなくイオン結合性もあるためヘキ開では単層が得られない。[NIMS中村G, 埼玉大上野G共同研究]

▲PVDにより単層SnS成長し、初めて2D面内強誘電特性を実証した。(東垂水君2020.3年修了) 応用物理学会講演奨励賞受賞2020.3, SSDM若手奨励賞受賞2020.9

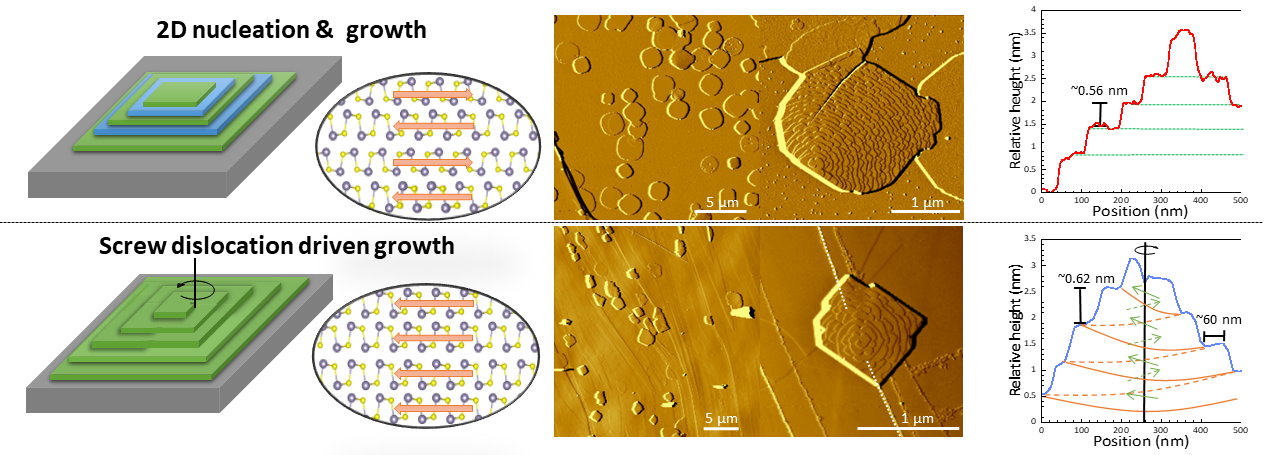

▲SnSは分極の向きが層ごとに逆向きになる偶奇効果を示すため、バルクにおいて強誘電/圧電特性を発現させるためには、分極の向きを揃える必要がある。通常2次元核生成・成長し、分極は打ち消しあうが、原子ステップのあるHOPG基板上に成長させた場合、スパイラル成長させることができ、分極を揃えることが可能になる(張君)。

Ref.

N. Higashitarumizu, H. Kawamoto, K. Ueno and K. Nagashio, "Fabrication and Surface Engineering of Two-Dimensional SnS Toward Piezoelectric Nanogenerator Application", MRS Advances, 2018, 3, 2809.

N. Higashitarumizu, H. Kawamoto, M. Nakamura, K. Shimamura, N. Ohashi, K. Ueno, and K. Nagashio, "Self-passivated ultra-thin SnS layers via mechanical exfoliation and post-oxidation", Nanoscale, 2018, 10, 22474.

H. Kawamoto, N. Higashitarumizu, N. Nagamura, M. Nakamura, K. Shimamura, N. Ohashi, and K. Nagashio, "Micrometer-scale monolayer SnS growth by physicalvapor deposition", Nanoscale, 2020, 12, 23274.

N. Higashitarumizu, H. Kawamoto, C.-J. Lee, B. -H. Lin, F. -H. Chu, I. Yonemori, T.i Nishimura, K. Wakabayashi, W. -H. Chang & K. Nagashio, "Purely in-plane ferroelectricity in monolayer SnS at room temperature", Nature commun.,2020, 11, 2428.

Yih-Ren Chang, Naoki Higashitarumizu, Hayami Kawamoto, Fu-Hsien Chu, Chien-Ju Lee, Tomonori Nishimura, Rong Xiang, Wen-Hao Chang, Shigeo Maruyama, Kosuke Nagashio, "Atomic-Step-Induced Screw-Dislocation-Driven Spiral Growth of SnS", Chem. Mater. 2021, 33, 1, 186–194.

Yih-Ren Chang, Tomonori Nishimura, Takashi Taniguchi, Kenji Watanabe,Kosuke Nagashio, “Performance enhancement of SnS/h-BN Heterostructure p-type FET via Thermodynamically Predicted Surface Oxide Conversion Method”, ACS Appl. Mater. Interfaces., 2022, 14, 17, 19928–19937.

Yih-Ren Chang, Ryo Nanae, Satsuki Kitamura, Tomonori Nishimura, Haonan Wang, Yubei Xiang, Keisuke Shinokita, Kazunari Matsuda, Takashi Taniguchi, Kenji Watanabe, and Kosuke Nagashio, “Shift current photovoltaics based on a noncentrosymmetric phase in in-plane ferroelectric SnS”, Adv. Mater., 2023, 35, 2301172.

Redhwan Moqbel, Yih-Ren Chang, Zi-Yi Li, Sheng-Hsun Kung, Hao-Yu Cheng, Chi-Cheng Lee, Kosuke Nagashio, Kung-Hsuan Lin, “Wavelength Dependence of Polarization-resolved Second Harmonic Generation from Ferroelectric SnS Few Layers”, 2D mater. 2023, 10, 015022.

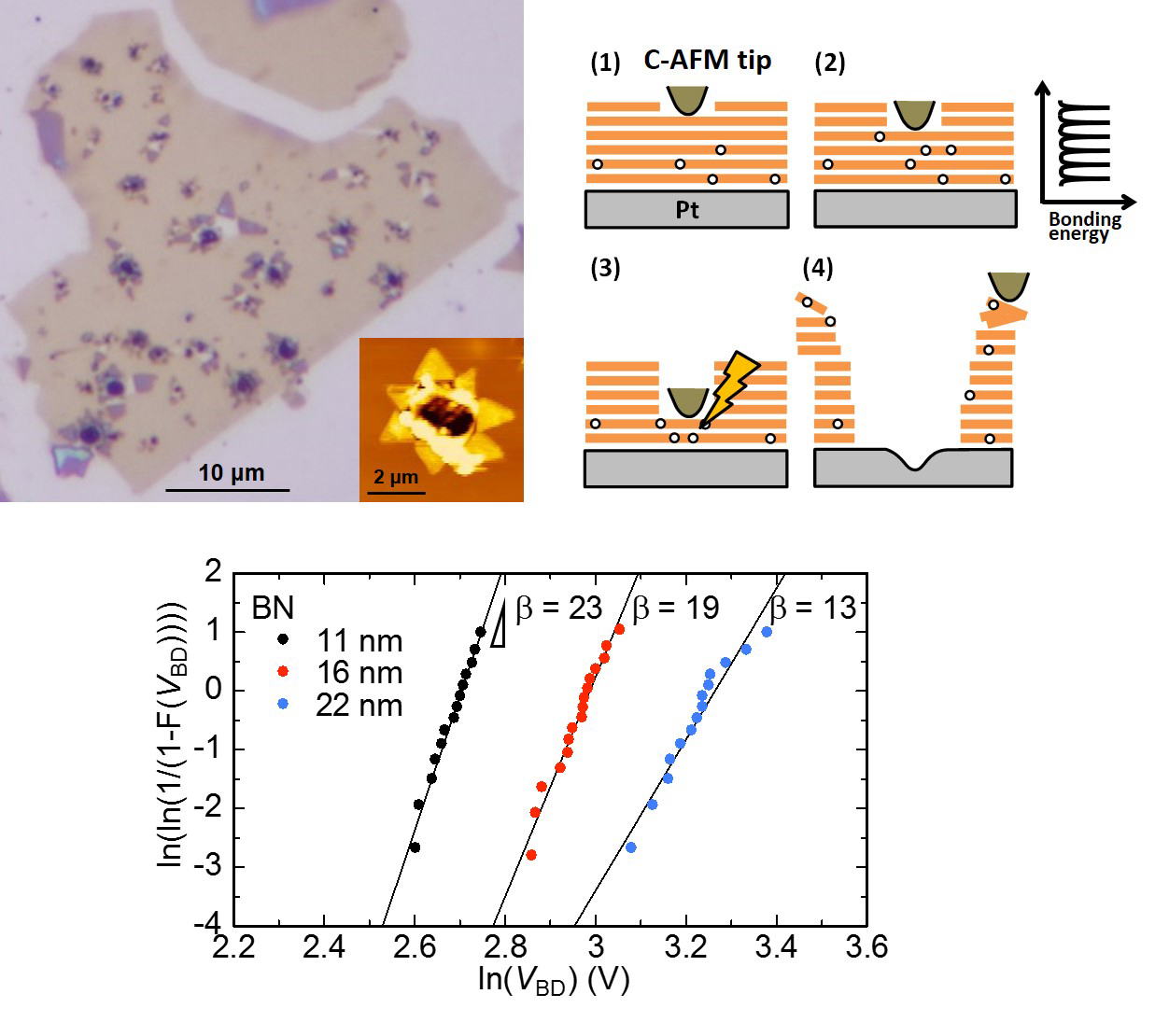

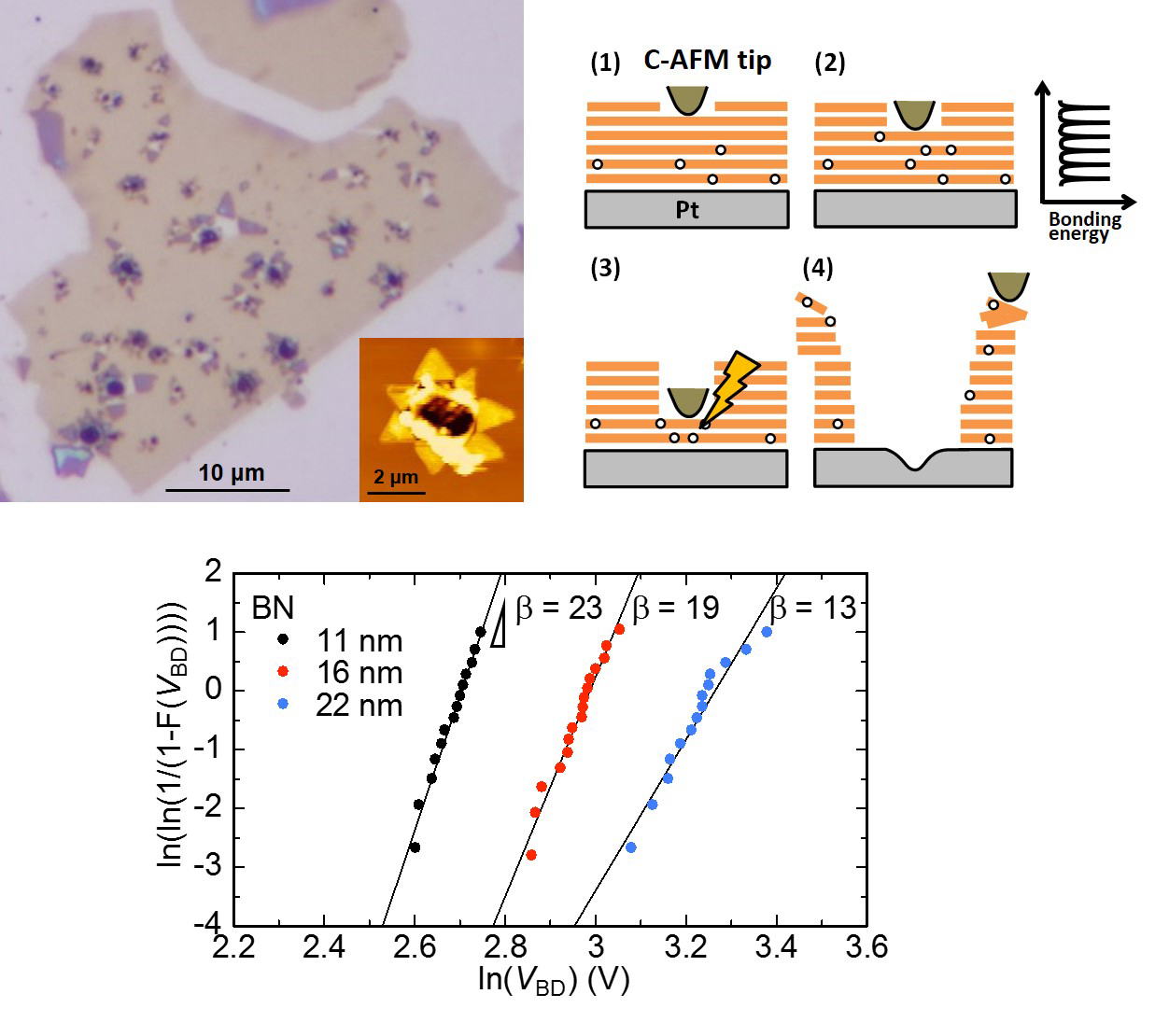

4. h-BNのlayer-by-layer絶縁破壊挙動とパワーデバイス展開

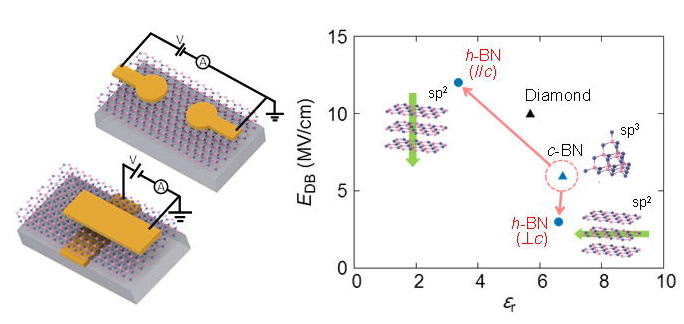

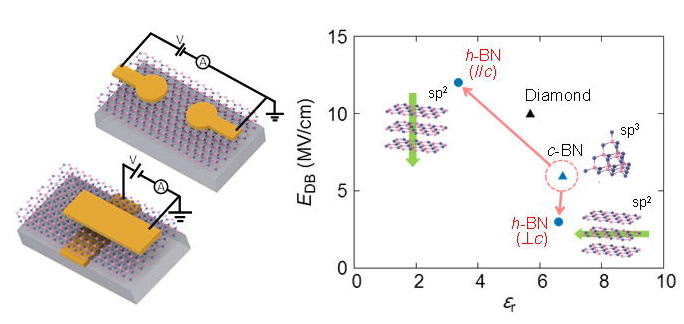

h-BNは層状チャネル材料に対して相互作用がほとんど無いため理想的な絶縁性基板と考えられますが、絶縁性に着目した研究はほとんどありません。コンダクティブAFMで、h-BNの絶縁破壊挙動を調べています。[NIMS谷口・渡邊G共同研究]

▲(左)絶縁破壊後の光学顕微鏡写真。挿入図のAFMからジグザグもしくはアームチェア端で破壊が進展していることがわかる。▲(右)面内共有結合、層間分子間力のため、周期的な結合エネルギーとなるため、layer-by-layerで上部から破壊が進む。▲(下)破壊電圧のWeibull plotから、欠陥形成位置の異方性が鍵であることがわかる。

▲(左)層に対して垂直と平行の電極を作成したデバイス。▲(右)絶縁破壊電界(EBD)と比誘電率の関係。sp3のc-BNからsp2のh-BNへの構造変化を考えた場合、面内の結合数を増加させることで、片方のEBDが弱くなることを認め、逆に垂直方向のEBDがダイアモンドより強くなる。(服部さん2016)応用物理学会講演奨励賞受賞2016.9

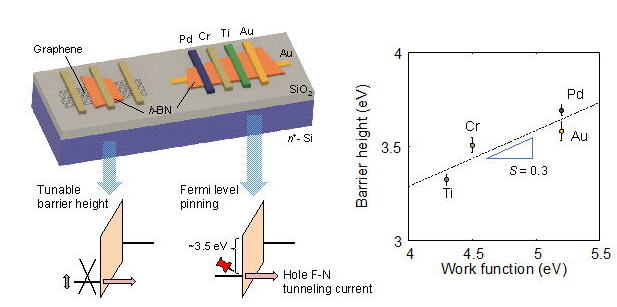

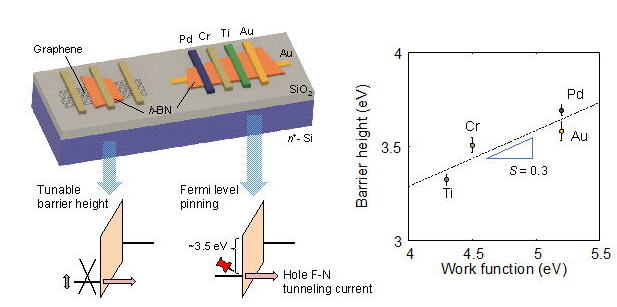

▲(左)仕事関数の異なる電極を並べたh-BNデバイス。▲(右)実験的に求めたバリア高さと仕事関数の関係。h-BNは絶縁体であるが、ピンニングを示すSファクターが0.3であり、強いフェルミレベルピンニングを示すことがわかった。(服部さん2017)

Ref.

Y. Hattori, T. Taniguchi, K. Watanabe, K. Nagashioi, "Layer-by-layer dielectric breakdown of hexagonal Boron Nitride", ACS nano, 2015, 9, 916.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, "Anisotropic breakdown strength of single crystal hexagonal Boron Nitride", ACS appl. mater. interfaces, 2016, 8, 27877.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, "Comparison of device structures for the dielectric breakdown measurement of hexagonal boron nitride", Appl. Phys. Lett., 2016, 109, 253111.

K. Nagashio, Y. Hattori, N. Takahashi, T. Taniguchi, K. Watanabe, J. Bao, W. Norimatsu, and M. Kusunoki, Electrical Integrity and Anisotropy in Dielectric Breakdown of Layered h-BN Insulator, ECS Transactions, 2017, 79, 91-97.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, “Impact ionization and transport properties of hexagonal boron nitride in constant-voltage measurement”, Phys. Rev. B, 2018, 97, 045425.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, "Determination of Carrier Polarity in Fowler-Nordheim Tunneling and Evidence of Fermi Level Pinning at the Hexagonal Boron Nitride/Metal Interface", ACS appl. mater. interfaces, 2018, 10, 11732.

Supawan Ngamprapawat, Tomonori Nishimura, Kenji Watanabe,Takashi Taniguchi, Kosuke Nagashio, “Current Injection into Single-crystalline Carbon-doped h-BN toward Electronic and Optoelectronic Applications”, ACS Appl. Mater. Interfaces., 2022, 14, 22, 25731–25740.

Supawan Ngamprapawat, Jimpei Kawase, Tomonori Nishimura, Kenji Watanabe, Takashi Taniguchi, and Kosuke Nagashio, ” From h-BN to graphene: characterizations of hybrid carbon-doped h-BN for applications in electronic and optoelectronic devices”, Adv. Electronic Mater., 2023, 2300083.

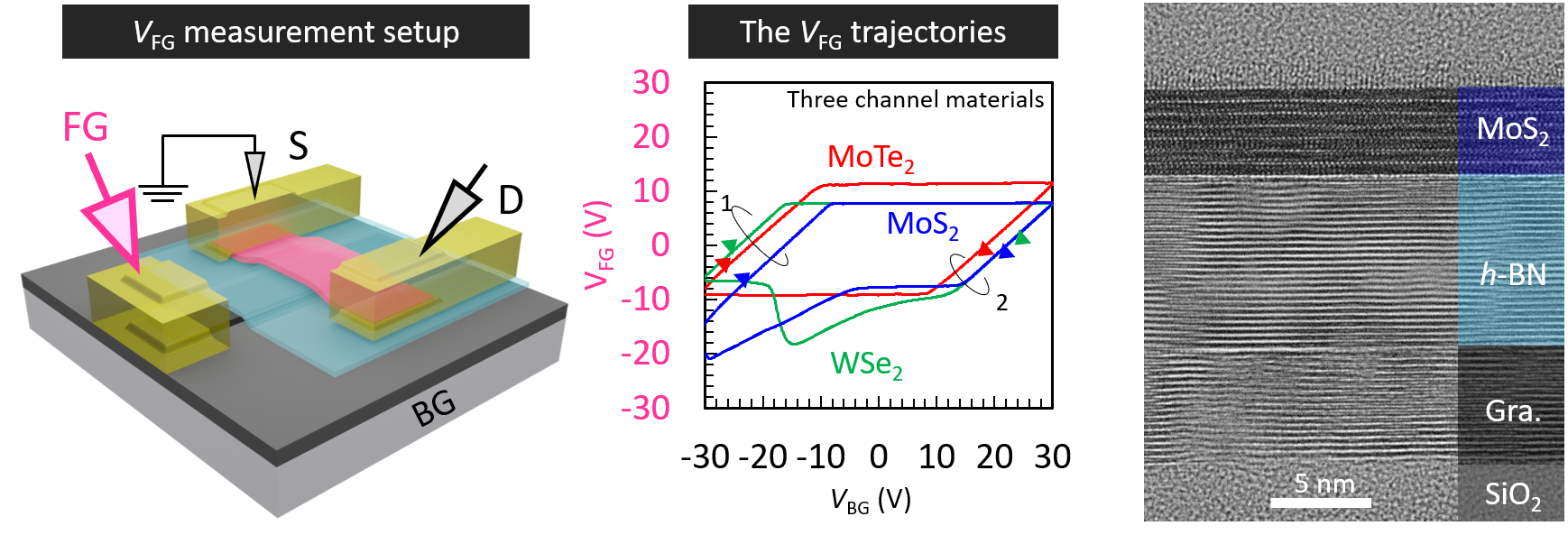

5. 2D flash memoryの動作機構

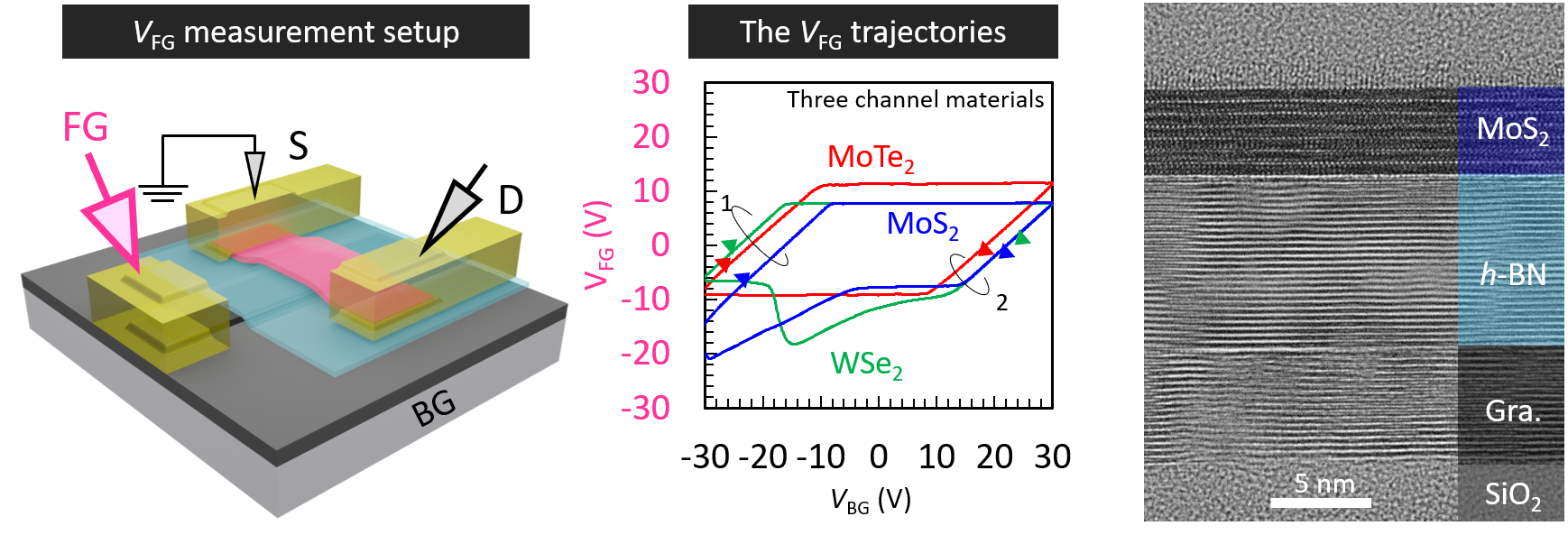

2Dヘテロ構造を利用したflash memoryは、ダングリングボンドフリーな界面のため高い電気的信頼性が得られることから期待が高い。しかしながら、2D flash memoryの動作については詳細な理解は得られていない。フローティングゲートに電極を形成し、書込、消去時のフローティングゲート電圧を計測することで動作機構の解明を試みている。

▲(左)フローティングゲート電圧の計測。(中)バックゲート掃引時のフローティングゲート電圧の軌跡。特徴的な3種類のチャネル材料に対して異なる軌跡を取り、詳細な解析からトンネル電流の律速場所が理解できる。(右)2Dヘテロの断面TEM。(佐々木君2021.9修了) SSDM若手奨励賞受賞2021.9

Ref.

T. Sasaki, K. Ueno, T. Taniguchi, K. Watanabe, T. Nishimura, K. Nagashio, "Material and Device Structure Designs for 2D Memory Devices Based on the Floating Gate Voltage Trajectory", ACS nano, 2021, 15, 6658.

T. Sasaki, K. Ueno, T. Taniguchi, K. Watanabe, T. Nishimura, and K. Nagashio, "Understanding the Memory Window Overestimation of 2D Materials Based Floating Gate Type Memory Devices by Measuring Floating Gate Voltage", small, 2020, 16, 2004907.

Taro Sasaki, Keiji Ueno, Takashi Taniguchi,Kenji Watanabe, Tomonori Nishimura, Kosuke Nagashio, “Ultrafast Operation of 2D Heterostructured Nonvolatile Memory Devices Provided by the Strong Short-Time Dielectric Breakdown Strength of h-BN”, ACS Appl. Mater. Interfaces., 2022, 14, 22, 25659–25669.

グラフェン及び2Dのデバイス化を目指した基礎物性評価

1. グラファイトからグラフェンへ

グラファイトをセロテープにて基板に転写しグラフェンFETを作成しています。

▲EBリソグラフィにより作成したグラフェンFETの光学顕微鏡写真(左)と概念図(右).

まずはグラファイトからグラフェンまでの全体像をつかむことが大切!

▲(左)層数の減少に伴いシート抵抗率が大きくシャープに。バンド構造を反映している。▲(右)層数の減少に伴い室温で規格化したシート抵抗率の温度依存性がグラファイトから2層まで連続的に変化。バンドオーバーラップの大きさを反映している。 (2011年 応用物理学会優秀論文賞)

ref.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Express, 2009, 2, 025003.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, Jpn. J. Appl. Phys. 2010, 49, 051304.

2. SiO2基板とグラフェンの相互作用

最も電気的信頼性あるSiO2基板には3種類の表面構造があり、グラフェンとの相互作用は大きく異なる!

▲表面構造により親水性と疎水性の作り分けが可能。転写によって得られるグラフェンサイズも異なる。(山下君, 2012修了)

▲親水性の場合は、ヒステリシスが観察されるが、疎水性表面では、ヒステリシスは観察されない。

ref.

K. Nagashio, T. Yamashita, T. Nishimura, K. Kita, and A. Toriumi, J. Appl. Phys. 2011, 110, 024513.

K. Nagashio, T. Yamashita, T. Nishimura, K. Kita, and A. Toriumi, "Impact of graphene/SiO2 interaction on FET mobility and Raman spectra in mechanically exforiated graphene films", IEEE International Electron device meeting (IEDM) Tech. Dig. 2010, 564.

3. グラフェン/金属界面でのコンタクト特性の理解と制御

いくらチャネル特性が良くても、コンタクト抵抗が最終的な律速過程となる可能性!

▲(左)6つの4端子デバイスを含むグラフェンデバイスの光学顕微鏡写真。電極はNi。▲(右)左のデバイスから見積もった2種類のコンタクト抵抗率(RcAとRcW)。エッジで決まるとして計算した場合、一定となり電流注入はエッジで起こっている。

金属と接触したグラフェンの状態密度は、化学吸着と物理吸着で大きく異なる!

▲(左)量子容量測定により金属と接したグラフェンの状態密度を抽出。Niとは化学吸着するためグラフェンの状態密度は増加している。一方、Auとは物理吸着するので、殆どグラフェンの状態密度は変化しない。▲(右)バックゲートで変調させて最も大きい状態密度と、その時のコンタクト抵抗率の相関性。グラフェンのコンタクト抵抗率は状態密度で律速されている。

井福君(2013.3修了), 応用物理学会講演奨励賞受賞2013.9

ref.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, "Metal/graphene contact as a performance killer of ultra-high mobility graphene – analysis of intrinsic mobility and contact resistance -", IEEE International Electron device meeting (IEDM) Tech. Dig. 2009, 565.

K. Nagashio, T. Moriyama, R. Ifuku, T. Nishimura, and A. Toriumi, "Is graphene contacting with metal still graphene?", IEEE International Electron device meeting (IEDM) Tech. Dig. 2011, 27.

K. Nagashio, R. Ifuku, T. Moriyama, T. Nishimura, and A. Toriumi, "Intrinsic graphene/metal contact", IEEE International Electron device meeting (IEDM) Tech. Dig. 2012, 68.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Lett. 2010, 97, 143514.

T. Moriyama, K. Nagashio, T. Nishimura, and A. Toriumi, J. Appl. Phys. 2013, 114, 024503.

R. Ifuku, K. Nagashio, T. Nishimura, and A. Toriumi, Appl. Phys. Lett. 2013, 103, 033514.

[Invited review] K. Nagashio, and A. Toriumi, Jpn. J. Appl. Phys. 2011, 50, 070108.

[Book] K. Nagashio, A. Toriumi, "Graphene/metal contact" in Frontiers of graphene and carbon nanotubes, Springer, 2015, pp.53-78.

4. 電気的信頼性あるhigh-kトップゲート絶縁膜形成と量子容量測定

グラフェンFETにおけるトップゲート絶縁膜として熱力学的考察からY2O3を選択し、高圧酸素アニールにより低電界リークの劇的な低下を達成しています。

▲(左)酸化の標準生成自由エネルギー変化。Yが最も酸化し易いことから、Y2O3を選択。▲(右)Y2O3トップゲート(~5nm)グラフェンFETを作成し、リーク電流密度を測定。Y2O3堆積後、1気圧酸素でアニール(AP-PDA)よりも100気圧酸素でアニール(HP-PDA)の方が低電界リークが減少。

▲CV測定から量子容量を抽出。トップゲート絶縁膜の高耐圧化によりグラフェンのフェルミエネルギーを0.5eV以上にまで変調できるように(金山君2015.3修了, 世界最高値)!

ref.

K. Kanayama, K. Nagashio, T. Nishimura, and A. Toriumi, Appl. Phys. Lett. 2014, 104, 083519.

K. Nagashio, T. Nishimura, and A. Toriumi, Appl. Phys. Lett. 2013, 102, 173507.

5. グラフェンのCVD成長低消費電力化につながるサブスレッショルド電圧の低減のためトンネルFETが注目を集めていますが、トンネル現象ゆえオン電流が小さいという欠点があります。理想的にはvad der Waals距離にまでトンネル距離を低減できる2次元層状へテロ構造を利用したトンネルFETを研究しています。[埼玉大上野G, NIMS谷口・渡邊G共同研究]

▲(左)p+-MoS2/n-MoS2とh-BNを組み合わせ完全2次元トンネルFETを形成した。(右)SSのId依存性。MOSFETの理論限界であるSS=60mV/decを切る値を達成。(中村君2020.3修了)

▲(左)ダイオード特性のゲートバイアス依存性からtypeIIからtypeIIIバンドアライメントへ変化していることがわかる。BTBTから拡散への変化も明確に観察される。(右)ダイオード特性の温度依存性から低温で負性微分抵抗(NDR)トレンドが観測されており、typeIIIでreverse側はバンド間トンネルであることがわかる。(中村君2020.3修了,何君2018.3修了)

▲(左)N+結晶候補としてSnSe2とPtS2のHall計測を行った結果、SnSe2は4.7*1018 cm-3であり、PtS2は3.6*1017 cm-3であった。SnSe2の方が高濃度結晶であり、活性化エネルギーも小さく低温でもキャリアが熱励起されていることからTFETのN+ソース結晶として適している。(右)SnSe2とPtS2のId-Vgからゲート変調しなくな膜厚を最大空乏層厚さと仮定した場合、ほぼ同じであるがバンドギャップの違いでキャリア数は異なる。(佐藤君2021.3修了)

Ref.

J. He, N. Fang, K. Nakamura, K. Ueno, T. Taniguchi, K. Watanabe, and K. Nagashio, "2-Dimensional Tunnel FETs with a Stable Charge-Transfer-Type p+-WSe₂ Source", Adv. Electronic Mater. 2018, 4, 1800207.

K. Nakamura, N. Nagamura, K. Ueno, T. Taniguchi, K. Watanabe, K. Nagashio, "All 2D heterostructure Tunnel Field Effect Transistors: Impact of Band Alignment and Heterointerface Quality", ACS Applied Materials & Interfaces, 2020, 12, 51598−51606.

Y. Sato, T. Nishimura, D. Duanfei, K. Ueno, K. Shinokita, K. Matsuda and K. Nagashio, "Intrinsic Electronic Transport Properties and Carrier Densities in PtS2 and SnSe2: Exploration of n+-Source for 2D Tunnel FETs", Adv. Electronic Mater., 2021, 7, 2100292.

Hiroto Ogura, Seiya Kawasaki, Zheng Liu, Takahiko Endo, Mina Maruyama,Yanlin Gao, Yusuke Nakanishi, Hong En Lim, Kazuhiro Yanagi, Toshifumi Irisawa, Keiji Ueno, Susumu Okada, Kosuke Nagashio, Yasumitsu Miyata, "Multilayer In-Plane Heterostructures Based on Transition Metal Dichalcogenides for Advanced Electronics", ACS nano, 2023, 17, 7, 6545-6554.

2. 2D材料(MoS2等)の成長・輸送特性・容量評価

バンドギャップを有する2次元層状物質であるMoS2は、単層で直接遷移型となるため、電子デバイスとしてだけでなく、光デバイスとしても注目されています。しかしながら、結晶性の良いKishグラファイトと比較して現時点では、結晶性の良いバルク結晶は育成できておらず、S欠陥が1013cm-2程度含まれることが知られています。この欠陥がどのように輸送特性に影響を与えるかを調べています。

▲(左)high-k/MoS2/SiO2スタックにおいて形成される界面凖位の3種類の起源。(中)MoS2は配位子場でバンドが決まる。Mo原子のd起動のスプリッティングで伝導帯と価電子帯が形成される。S欠陥凖位はミッドギャップ及び価電子帯側に形成される。(左)伝導帯側は、2Dヘテロで原子レベルでフラットな界面を形成すれば、歪による凖位は低減される。一方、価電子帯側は、S欠陥凖位のため界面凖位が高くヘテロを組んでも改善されない。(方楠君&豊田君2019.3修了)

▲(左)単層MoS2の量子容量(CQ)の温度依存性。界面凖位がメインとなる低C領域よりも大きいCQ領域においては理論との良い一致を示している。原子レベルで薄いMoS2では、C-V測定はMoS2の量子容量で決定されることがわかる。(方楠君2019.3修了)応用物理学会講演奨励賞受賞2018.3

▲(左)石英上に作成したMoS2FETデバイス。(中)。Si基板上と比較して浮遊容量がほぼ消滅しており、容量計測では石英基板が必須である。(右)多層MoS2の容量計測結果。石英基板であるため、空乏側を正確に決めることができる。

▲(左)B1530A WGFMUを用いて単層MoS2にTime domain charge pumping法を適応した。(右)界面での電子トラップとデトラップを初めて観測した。(谷口君2018.3修了)

▲(左)単層MoS2 FETの温度依存性。温度の低下と共にトランスファー曲線がギザギザになる。(右)ギザギザのでるゲートバイアスで電流の時間変化を追うとランダムテレグラフノイズ(RTN)が観測される。多端子デバイス解析から電子が欠陥にトラップされる挙動を観測していることがわかった。(方楠君2019.3修了)SSDM若手奨励賞受賞2016.9

▲(左)CVD成長したMoS2の上側と下側のSのどちらが欠陥が多いかを通常転写と反転転写により輸送特性を評価した。(右)どちらも金属絶縁体遷移が観測され、他の報告と比較して高い移動度を示したことから、輸送現象からは上下の結晶性に観測できるほどの差は認められなかった。(倉林君2017.3修了)

Ref.

S. Kurabayashi, and K. Nagashio, ”Transport properties of the top and bottom surfaces in monolayer MoS2 grown by chemical vapor deposition”, Nanoscale, 2017, 9, 13264-13271.

N. Fang, K. Nagashio, and A. Toriumi, "Subthreshold transport in mono- and multilayered MoS2 FETs", Appl. Phys. Express, 2015, 8, 065203.

N. Fang, K. Nagashio, and A. Toriumi, "Experimental detection of active defects in few layers MoS2 through random telegraphic signals analysis observed in its FET characteristics", 2D mater., 2017, 4, 015035.

N. Fang, K. Nagashio, "Band tail interface states and quantum capacitance in a monolayer molybdenum disulfide field-effect-transistor", J. Phys. D, 2018, 51, 065110.

N. Fang, and K. Nagashio, "Accumulation-mode two-dimensional field-effect transistor: Operation mechanism and thickness scaling rule", ACS appl. mater. interfaces, 2018, 10, 32355.

K. Taniguchi, N. Fang, and K. Nagashio, "Direct observation of electron capture & emission processes by the time domain charge pumping measurement of MoS2 FET", Appl. Phys. Lett. 2018, 113, 133505.

W. Li, et al., "Uniform and ultrathin high-κ gate dielectrics for two-dimensional electronic devices", Nature Electronics, 2019, 2, 563–571.

N. Fang, S. Toyoda, T. Taniguchi, K. Watanabe, and K. Nagashio, "Full energy spectra of interface state densities for n– and p-type MoS2 field-effect transistors", Adv. Func. Mater. 2019, 29, 1904465.

N. Fang and K. Nagashio, "Quantum-mechanical effect in atomically thin MoS2 FET", 2D mater, 2020, 7, 014001.

Ryoichi Kato, Haruki Uchiyama, Tomonori Nishimura, Keiji Ueno, Takashi Taniguchi, Kenji Watanabe, Edward Chen, Kosuke Nagashio, “p-type conversion of WS2 and WSe2 by position-selective oxidation doping and its application in top gate transistors”, ACS appl. mater. interfaces, 2023, 15(22), 26977-26984.

3. 環境発電を目指した圧電/強誘電2次元SnS

2次元層状物質の中には圧電特性を示すものがあり非点対称性の単層SnSはPZTと同等の圧電定数dを有することが理論的に予測されている。層間力はvdWだけでなくイオン結合性もあるためヘキ開では単層が得られない。[NIMS中村G, 埼玉大上野G共同研究]

▲PVDにより単層SnS成長し、初めて2D面内強誘電特性を実証した。(東垂水君2020.3年修了) 応用物理学会講演奨励賞受賞2020.3, SSDM若手奨励賞受賞2020.9

▲SnSは分極の向きが層ごとに逆向きになる偶奇効果を示すため、バルクにおいて強誘電/圧電特性を発現させるためには、分極の向きを揃える必要がある。通常2次元核生成・成長し、分極は打ち消しあうが、原子ステップのあるHOPG基板上に成長させた場合、スパイラル成長させることができ、分極を揃えることが可能になる(張君)。

Ref.

N. Higashitarumizu, H. Kawamoto, K. Ueno and K. Nagashio, "Fabrication and Surface Engineering of Two-Dimensional SnS Toward Piezoelectric Nanogenerator Application", MRS Advances, 2018, 3, 2809.

N. Higashitarumizu, H. Kawamoto, M. Nakamura, K. Shimamura, N. Ohashi, K. Ueno, and K. Nagashio, "Self-passivated ultra-thin SnS layers via mechanical exfoliation and post-oxidation", Nanoscale, 2018, 10, 22474.

H. Kawamoto, N. Higashitarumizu, N. Nagamura, M. Nakamura, K. Shimamura, N. Ohashi, and K. Nagashio, "Micrometer-scale monolayer SnS growth by physicalvapor deposition", Nanoscale, 2020, 12, 23274.

N. Higashitarumizu, H. Kawamoto, C.-J. Lee, B. -H. Lin, F. -H. Chu, I. Yonemori, T.i Nishimura, K. Wakabayashi, W. -H. Chang & K. Nagashio, "Purely in-plane ferroelectricity in monolayer SnS at room temperature", Nature commun.,2020, 11, 2428.

Yih-Ren Chang, Naoki Higashitarumizu, Hayami Kawamoto, Fu-Hsien Chu, Chien-Ju Lee, Tomonori Nishimura, Rong Xiang, Wen-Hao Chang, Shigeo Maruyama, Kosuke Nagashio, "Atomic-Step-Induced Screw-Dislocation-Driven Spiral Growth of SnS", Chem. Mater. 2021, 33, 1, 186–194.

Yih-Ren Chang, Tomonori Nishimura, Takashi Taniguchi, Kenji Watanabe,Kosuke Nagashio, “Performance enhancement of SnS/h-BN Heterostructure p-type FET via Thermodynamically Predicted Surface Oxide Conversion Method”, ACS Appl. Mater. Interfaces., 2022, 14, 17, 19928–19937.

Yih-Ren Chang, Ryo Nanae, Satsuki Kitamura, Tomonori Nishimura, Haonan Wang, Yubei Xiang, Keisuke Shinokita, Kazunari Matsuda, Takashi Taniguchi, Kenji Watanabe, and Kosuke Nagashio, “Shift current photovoltaics based on a noncentrosymmetric phase in in-plane ferroelectric SnS”, Adv. Mater., 2023, 35, 2301172.

Redhwan Moqbel, Yih-Ren Chang, Zi-Yi Li, Sheng-Hsun Kung, Hao-Yu Cheng, Chi-Cheng Lee, Kosuke Nagashio, Kung-Hsuan Lin, “Wavelength Dependence of Polarization-resolved Second Harmonic Generation from Ferroelectric SnS Few Layers”, 2D mater. 2023, 10, 015022.

4. h-BNのlayer-by-layer絶縁破壊挙動とパワーデバイス展開

h-BNは層状チャネル材料に対して相互作用がほとんど無いため理想的な絶縁性基板と考えられますが、絶縁性に着目した研究はほとんどありません。コンダクティブAFMで、h-BNの絶縁破壊挙動を調べています。[NIMS谷口・渡邊G共同研究]

▲(左)絶縁破壊後の光学顕微鏡写真。挿入図のAFMからジグザグもしくはアームチェア端で破壊が進展していることがわかる。▲(右)面内共有結合、層間分子間力のため、周期的な結合エネルギーとなるため、layer-by-layerで上部から破壊が進む。▲(下)破壊電圧のWeibull plotから、欠陥形成位置の異方性が鍵であることがわかる。

▲(左)層に対して垂直と平行の電極を作成したデバイス。▲(右)絶縁破壊電界(EBD)と比誘電率の関係。sp3のc-BNからsp2のh-BNへの構造変化を考えた場合、面内の結合数を増加させることで、片方のEBDが弱くなることを認め、逆に垂直方向のEBDがダイアモンドより強くなる。(服部さん2016)応用物理学会講演奨励賞受賞2016.9

▲(左)仕事関数の異なる電極を並べたh-BNデバイス。▲(右)実験的に求めたバリア高さと仕事関数の関係。h-BNは絶縁体であるが、ピンニングを示すSファクターが0.3であり、強いフェルミレベルピンニングを示すことがわかった。(服部さん2017)

Ref.

Y. Hattori, T. Taniguchi, K. Watanabe, K. Nagashioi, "Layer-by-layer dielectric breakdown of hexagonal Boron Nitride", ACS nano, 2015, 9, 916.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, "Anisotropic breakdown strength of single crystal hexagonal Boron Nitride", ACS appl. mater. interfaces, 2016, 8, 27877.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, "Comparison of device structures for the dielectric breakdown measurement of hexagonal boron nitride", Appl. Phys. Lett., 2016, 109, 253111.

K. Nagashio, Y. Hattori, N. Takahashi, T. Taniguchi, K. Watanabe, J. Bao, W. Norimatsu, and M. Kusunoki, Electrical Integrity and Anisotropy in Dielectric Breakdown of Layered h-BN Insulator, ECS Transactions, 2017, 79, 91-97.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, “Impact ionization and transport properties of hexagonal boron nitride in constant-voltage measurement”, Phys. Rev. B, 2018, 97, 045425.

Y. Hattori, T. Taniguchi, K. Watanabe, and K. Nagashio, "Determination of Carrier Polarity in Fowler-Nordheim Tunneling and Evidence of Fermi Level Pinning at the Hexagonal Boron Nitride/Metal Interface", ACS appl. mater. interfaces, 2018, 10, 11732.

Supawan Ngamprapawat, Tomonori Nishimura, Kenji Watanabe,Takashi Taniguchi, Kosuke Nagashio, “Current Injection into Single-crystalline Carbon-doped h-BN toward Electronic and Optoelectronic Applications”, ACS Appl. Mater. Interfaces., 2022, 14, 22, 25731–25740.

Supawan Ngamprapawat, Jimpei Kawase, Tomonori Nishimura, Kenji Watanabe, Takashi Taniguchi, and Kosuke Nagashio, ” From h-BN to graphene: characterizations of hybrid carbon-doped h-BN for applications in electronic and optoelectronic devices”, Adv. Electronic Mater., 2023, 2300083.

5. 2D flash memoryの動作機構

2Dヘテロ構造を利用したflash memoryは、ダングリングボンドフリーな界面のため高い電気的信頼性が得られることから期待が高い。しかしながら、2D flash memoryの動作については詳細な理解は得られていない。フローティングゲートに電極を形成し、書込、消去時のフローティングゲート電圧を計測することで動作機構の解明を試みている。

▲(左)フローティングゲート電圧の計測。(中)バックゲート掃引時のフローティングゲート電圧の軌跡。特徴的な3種類のチャネル材料に対して異なる軌跡を取り、詳細な解析からトンネル電流の律速場所が理解できる。(右)2Dヘテロの断面TEM。(佐々木君2021.9修了) SSDM若手奨励賞受賞2021.9

Ref.

T. Sasaki, K. Ueno, T. Taniguchi, K. Watanabe, T. Nishimura, K. Nagashio, "Material and Device Structure Designs for 2D Memory Devices Based on the Floating Gate Voltage Trajectory", ACS nano, 2021, 15, 6658.

T. Sasaki, K. Ueno, T. Taniguchi, K. Watanabe, T. Nishimura, and K. Nagashio, "Understanding the Memory Window Overestimation of 2D Materials Based Floating Gate Type Memory Devices by Measuring Floating Gate Voltage", small, 2020, 16, 2004907.

Taro Sasaki, Keiji Ueno, Takashi Taniguchi,Kenji Watanabe, Tomonori Nishimura, Kosuke Nagashio, “Ultrafast Operation of 2D Heterostructured Nonvolatile Memory Devices Provided by the Strong Short-Time Dielectric Breakdown Strength of h-BN”, ACS Appl. Mater. Interfaces., 2022, 14, 22, 25659–25669.

グラフェン及び2Dのデバイス化を目指した基礎物性評価

1. グラファイトからグラフェンへ

グラファイトをセロテープにて基板に転写しグラフェンFETを作成しています。

▲EBリソグラフィにより作成したグラフェンFETの光学顕微鏡写真(左)と概念図(右).

まずはグラファイトからグラフェンまでの全体像をつかむことが大切!

▲(左)層数の減少に伴いシート抵抗率が大きくシャープに。バンド構造を反映している。▲(右)層数の減少に伴い室温で規格化したシート抵抗率の温度依存性がグラファイトから2層まで連続的に変化。バンドオーバーラップの大きさを反映している。 (2011年 応用物理学会優秀論文賞)

ref.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Express, 2009, 2, 025003.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, Jpn. J. Appl. Phys. 2010, 49, 051304.

2. SiO2基板とグラフェンの相互作用

最も電気的信頼性あるSiO2基板には3種類の表面構造があり、グラフェンとの相互作用は大きく異なる!

▲表面構造により親水性と疎水性の作り分けが可能。転写によって得られるグラフェンサイズも異なる。(山下君, 2012修了)

▲親水性の場合は、ヒステリシスが観察されるが、疎水性表面では、ヒステリシスは観察されない。

ref.

K. Nagashio, T. Yamashita, T. Nishimura, K. Kita, and A. Toriumi, J. Appl. Phys. 2011, 110, 024513.

K. Nagashio, T. Yamashita, T. Nishimura, K. Kita, and A. Toriumi, "Impact of graphene/SiO2 interaction on FET mobility and Raman spectra in mechanically exforiated graphene films", IEEE International Electron device meeting (IEDM) Tech. Dig. 2010, 564.

3. グラフェン/金属界面でのコンタクト特性の理解と制御

いくらチャネル特性が良くても、コンタクト抵抗が最終的な律速過程となる可能性!

▲(左)6つの4端子デバイスを含むグラフェンデバイスの光学顕微鏡写真。電極はNi。▲(右)左のデバイスから見積もった2種類のコンタクト抵抗率(RcAとRcW)。エッジで決まるとして計算した場合、一定となり電流注入はエッジで起こっている。

金属と接触したグラフェンの状態密度は、化学吸着と物理吸着で大きく異なる!

▲(左)量子容量測定により金属と接したグラフェンの状態密度を抽出。Niとは化学吸着するためグラフェンの状態密度は増加している。一方、Auとは物理吸着するので、殆どグラフェンの状態密度は変化しない。▲(右)バックゲートで変調させて最も大きい状態密度と、その時のコンタクト抵抗率の相関性。グラフェンのコンタクト抵抗率は状態密度で律速されている。

井福君(2013.3修了), 応用物理学会講演奨励賞受賞2013.9

ref.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, "Metal/graphene contact as a performance killer of ultra-high mobility graphene – analysis of intrinsic mobility and contact resistance -", IEEE International Electron device meeting (IEDM) Tech. Dig. 2009, 565.

K. Nagashio, T. Moriyama, R. Ifuku, T. Nishimura, and A. Toriumi, "Is graphene contacting with metal still graphene?", IEEE International Electron device meeting (IEDM) Tech. Dig. 2011, 27.

K. Nagashio, R. Ifuku, T. Moriyama, T. Nishimura, and A. Toriumi, "Intrinsic graphene/metal contact", IEEE International Electron device meeting (IEDM) Tech. Dig. 2012, 68.

K. Nagashio, T. Nishimura, K. Kita, and A. Toriumi, Appl. Phys. Lett. 2010, 97, 143514.

T. Moriyama, K. Nagashio, T. Nishimura, and A. Toriumi, J. Appl. Phys. 2013, 114, 024503.

R. Ifuku, K. Nagashio, T. Nishimura, and A. Toriumi, Appl. Phys. Lett. 2013, 103, 033514.

[Invited review] K. Nagashio, and A. Toriumi, Jpn. J. Appl. Phys. 2011, 50, 070108.

[Book] K. Nagashio, A. Toriumi, "Graphene/metal contact" in Frontiers of graphene and carbon nanotubes, Springer, 2015, pp.53-78.

4. 電気的信頼性あるhigh-kトップゲート絶縁膜形成と量子容量測定

グラフェンFETにおけるトップゲート絶縁膜として熱力学的考察からY2O3を選択し、高圧酸素アニールにより低電界リークの劇的な低下を達成しています。

▲(左)酸化の標準生成自由エネルギー変化。Yが最も酸化し易いことから、Y2O3を選択。▲(右)Y2O3トップゲート(~5nm)グラフェンFETを作成し、リーク電流密度を測定。Y2O3堆積後、1気圧酸素でアニール(AP-PDA)よりも100気圧酸素でアニール(HP-PDA)の方が低電界リークが減少。

▲CV測定から量子容量を抽出。トップゲート絶縁膜の高耐圧化によりグラフェンのフェルミエネルギーを0.5eV以上にまで変調できるように(金山君2015.3修了, 世界最高値)!

ref.

K. Kanayama, K. Nagashio, T. Nishimura, and A. Toriumi, Appl. Phys. Lett. 2014, 104, 083519.

K. Nagashio, T. Nishimura, and A. Toriumi, Appl. Phys. Lett. 2013, 102, 173507.

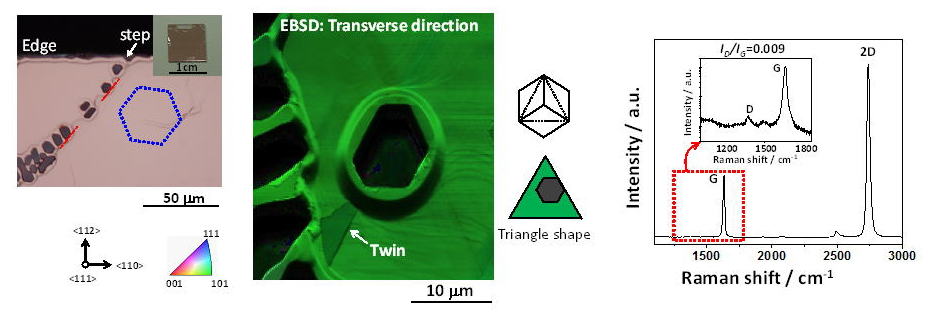

マイカ基板上に単結晶Cu(111)を堆積することにより方位の揃ったグラフェンを成長。

▲(左)CVDにより成長させたグラフェンをSiO2上に転写しラマンにより結晶性の評価。欠陥に起因するDバンドをログスケールでやっと見える程度にまで低減。▲(右)4端子測定により移動度の評価。最高で4,500cm2/Vs程度を得ている。(Qiさん, 2013)

Ref.

J. L. Qi, K. Nagashio, T. Nishimura, A. Toriumi, "Crystal orientation and macroscopic surface roughness in hetero-epitaxially grown graphene on Cu/mica", Nanotechnology, 2014, 25, 185602.

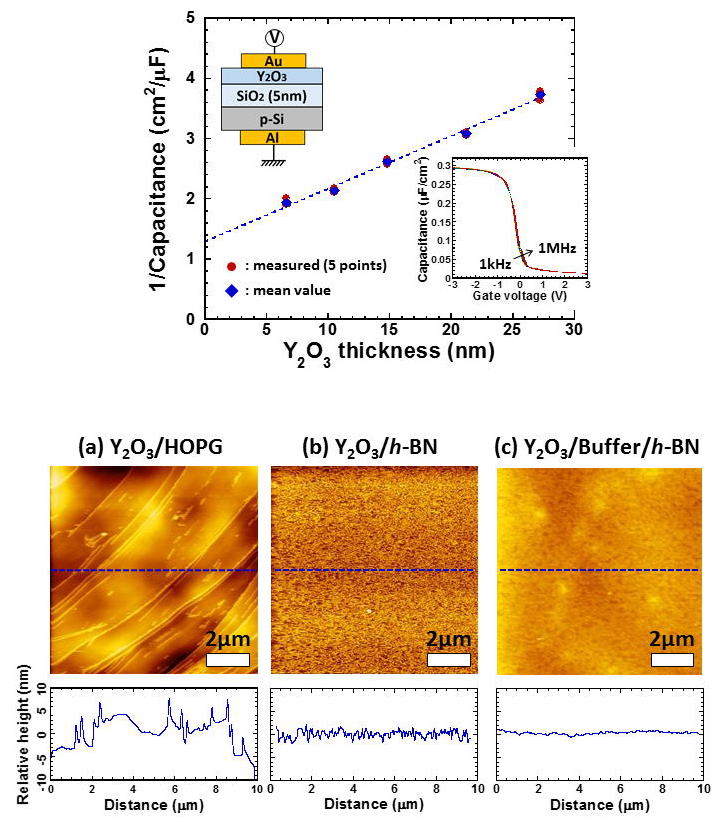

6. ALDによる層状物質への絶縁膜堆積

グラフェンに代表される層状物質系では、表面にダングリングボンドが無いので、原子層堆積法(ALD)が困難です。h-BNでは結合に極性を有していることから、プリカーサーが物理吸着します。これを利用してALDによる直接堆積を狙っています。

▲(上)SiO2上に堆積したALD-Y2O3の膜厚に対する1/Cプロット。挿入図は容量測定。傾きからY2O3の誘電率をk=12.9と見積もることができる。▲(下)HOPG上(a), h-BN上(b)、バッファー層有りのh-BN上(c)に堆積したALD-Y2O3。HOPGよりもh-BNの方が直接堆積が容易。ただし、トップゲートとして利用するためにリーク電流を低減させるためには、バッファー層の形成が必要である。(高橋君2016.3修了)

Ref.

N. Takahashi, T. Taniguchi, K. Watanabe, K. Nagashioi, "Atomic layer deposition of Y2O3 on h-BN for a gate stack in graphene FETs", Nanotechnology, 2015, 26, 175708.

N. Takahashi, and K. Nagashio, "Buffer Layer Engineering on Graphene via Various Oxidation Methods for Atomic Layer Deposition", Appl. Phys. Express, 2016, 9, 125101.

7. 2層グラフェンの輸送特性とギャップ内準位計測

A. high-k Y2O3 topgate

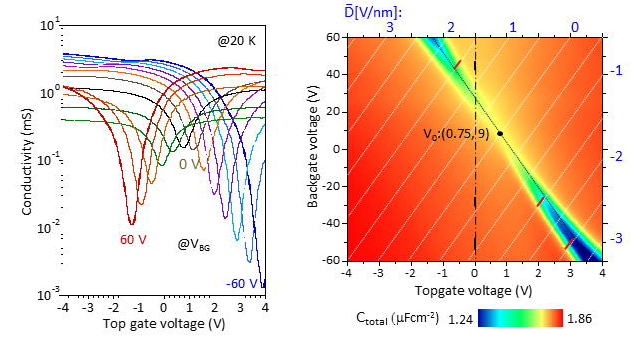

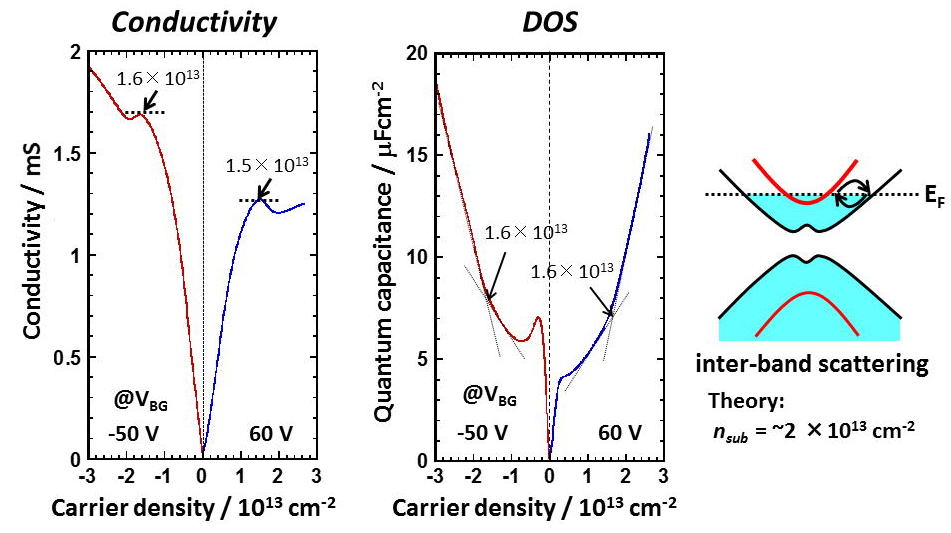

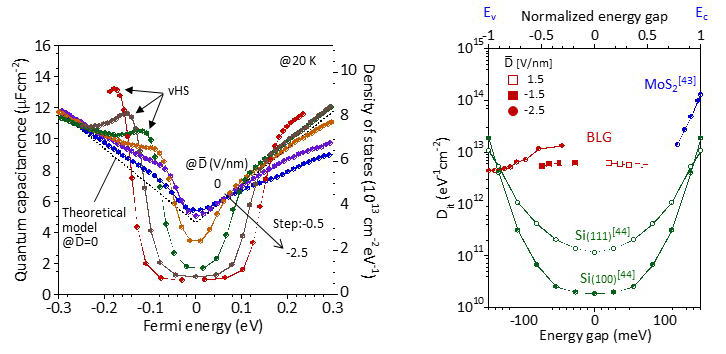

2層グラフェンでは、外部電界でギャップが形成されますが、ギャップ内準位のためIon/offが小さいことが良く知られています。高圧酸化で抗耐圧化したY2O3トップゲートによるIon/offの改善を行い、今回初めてギャップ内準位の定量的評価を行いました。

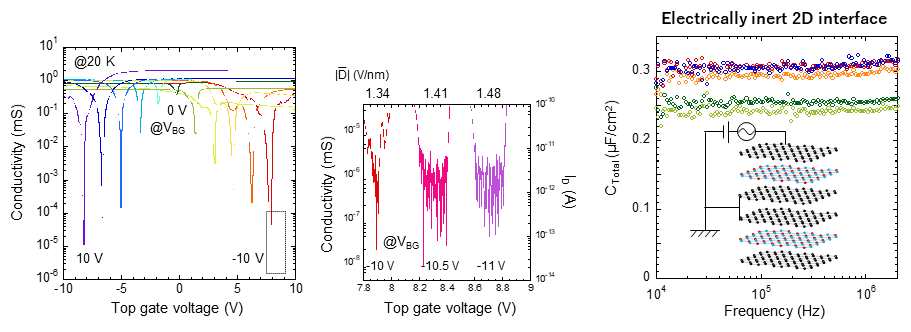

▲(左)コンダクティビティとゲート電圧の関係。Ion/off=3*103を達成@VBG=-60V。(右)ソース-トップゲート間の全容量3Dマップ。ギャップ形成に伴い状態密度の低下による容量低減が観察される。

▲抗耐圧化したY2O3トップゲートでは、フェルミレベルをupper subbandまで変調できる。コンダクティビティにおいてはsubband散乱による低下、量子容量計測においては、upper subbandに入ったことによる状態密度の傾きの変化が同じキャリア数で観察される。

▲(左)2層グラフェンの量子容量計測によるバンドギャップ計測。(右)コンダクタンス法により計測したギャップ内準位。ギャップ内準位の起源は、絶縁膜界面のトラップサイトもしくは、ABスタックの乱れによると考えている。(金山君2015.3修了)

B. 完全2次元層状へテロ

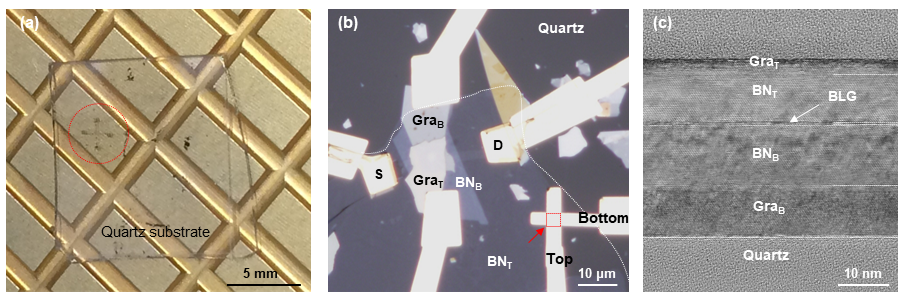

high-k Y2O3では、荷電不純物の影響のためギャップが空間的に均一に形成されない。そこで、絶縁体はh-BN、ゲート電極はグラファイトを用いることで完全2次元層状へテロ2層グラフェンFETを作成した。

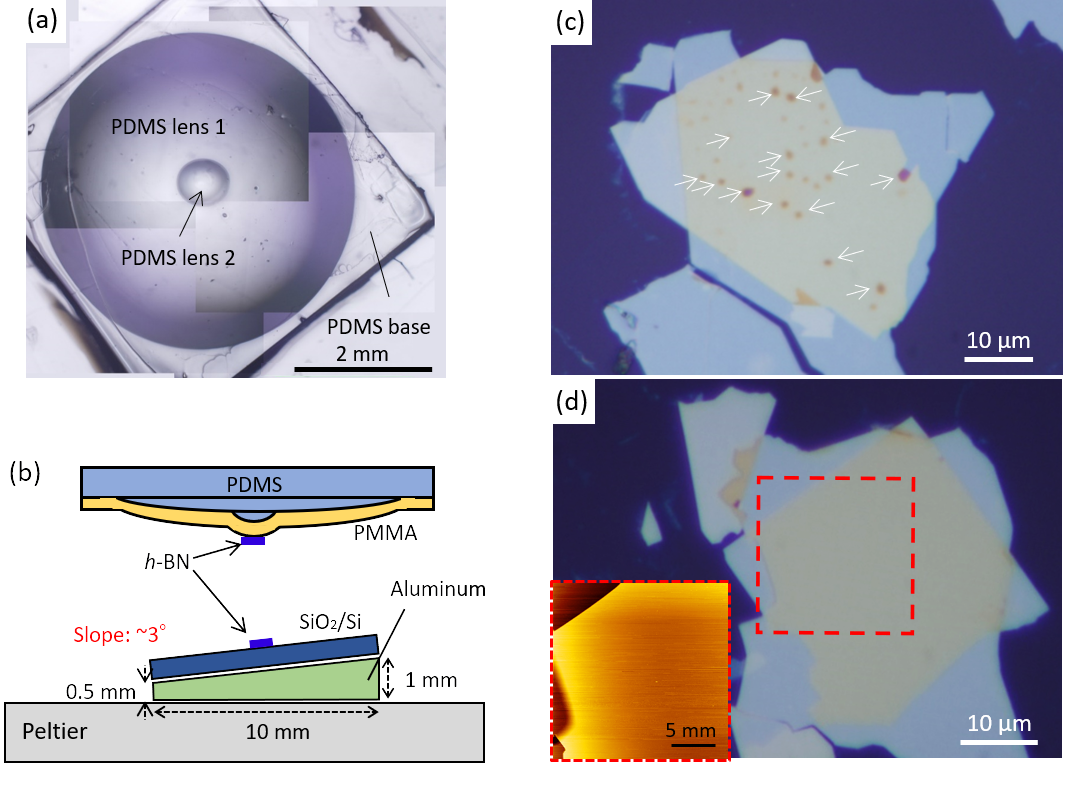

▲(左)容量の周波数依存性の精密計測には浮遊容量の低減が必須であり、石英基板を使用している。(中)完全2次元層状へテロデバイス。(右)TEMによる断面写真。バブルフリーの清浄界面が得られている。

▲(左)非常に高いon/offを得ている(@EG = ~100 meV)。(中)拡大すると計測器の測定限界に到達している。(右)トップゲート容量の周波数依存性は観測されない。バブルが存在する場合には、コンダクタンス法でピークが観測されるが、バブルフリーの清浄界面では、ピークは観測されないことから、界面準位は計測限界以下である。(ウワンノー君2020.3修了)

Ref.

[Review] K. Nagashio, "Graphene field-effect transistor application -Electric band structure of graphene in transistor structure extracted from quantum capacitance-", J. Mater. Res. 2017, 32, 64.

K. Kanayama, and K. Nagashio, "Gap state analysis in electric-field-induced band gap for bilayer graphene", Sic. Rep. 2015,5, 15789.

K. Nagashio, K. Kanayama, T. Nishimura, and A. Toriumi, “Quantum capacitance measurement of bilayer graphene”, ECS Trans. 2014, 61(3), 75.

K. Nagashio, K. Kanayama, T. Nishimura, and A. Toriumi, "Carrier response in band gap and multiband transport in bilayer graphene under the ultra-high displancement", IEEE International Electron device meeting (IEDM) Tech. Dig. 2013, 503.

T. Uwanno, T. Taniguchi, K. Watanabe, & K. Nagashio, "Electrically inert h-BN/bilayer graphene interface in all-2D-heterostructure FETs", ACS appl. mater. interfaces, 2018, 10, 28780.

8. 2Dヘテロ構造作製のための完全乾式バブルフリー転写技術

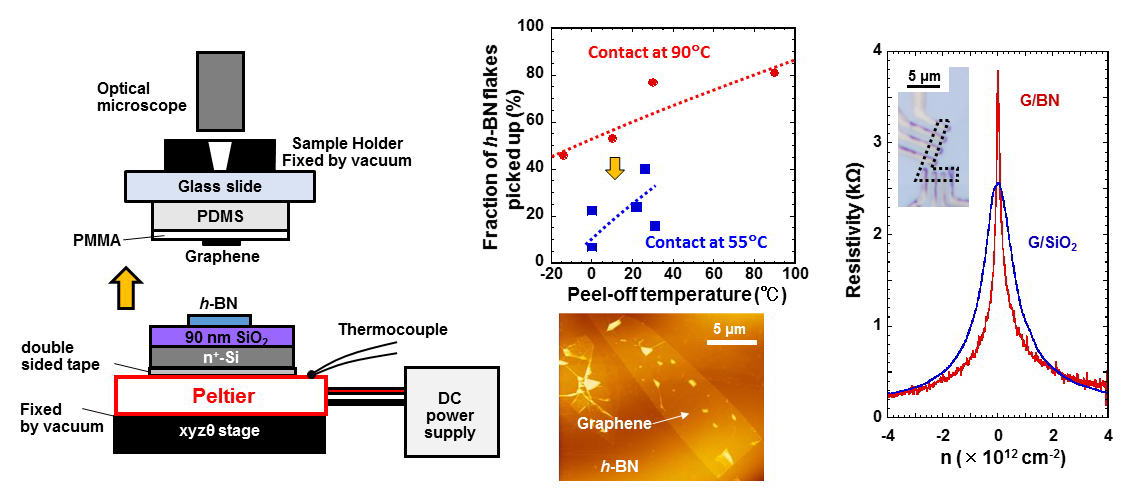

SiO2上2層グラフェンのギャップ内準位計測結果から、デバイス研究においてもh-BNとの複層化が必要となっています。通常、位置あわせ後、PMMAを溶融してデバイス作成を行いますが、輸送特性に残渣の影響が問題となります。無機/有機の熱膨張率の違いを利用して完全乾式での転写技術を確立しました。

▲(左)ペルチェによる温度可変の転写装置。(中)接触時の最適温度は55C, 剥離時の最適温度は15Cである。PMMA残渣がなくグラフェン/h-BN界面にトラップされたhydrocarbon系のバブルがきれいにみえる。(右)輸送特性。SiO2上とh-BN上を比較すると、h-BNの方で移動度の向上が観察される。(ウワンノー君2020.3修了)

▲(a)PDMSをレンズ形状に固めピンポイント積層を可能に。(a)積層時に一方向に接触界面をスイープさせるためにスロープを使う。(c)スロープ無しでの積層では、バブルが入り込む。(d)スロープの利用によりバブルフリー積層を達成。(豊田君2019.3修了)

Ref.

T. Uwanno, Y. Hattori, T Taniguchi, K Watanabe and K Nagashio, "Fully dry PMMA transfer of graphene on h-BN using a heating/cooling system", 2D mater. 2015, 2, 041002. Highlight of 2015

S. Toyoda, T. Uwanno, T. Taniguchi, K. Watanabe, and K. Nagashio, "Pinpoint pick-up and bubble-free assembly of 2D materials using PDMS/PMMA polymers with lens shapes", Appl. Phys. Express, 2019, 12, 055008.

9. TiOxナノシートの電子輸送特性評価

high-k酸化物ナノシートのゲート絶縁膜展開及びナノシート自身のFET応用を目指して研究しています。[NIMS長田G共同研究]

」

」▲(左)TiOxナノシートをアニールによりアナターゼに固相変態させn型FETとしての動作を確認した。(右)TiOxナノシートは、過剰TiのためO空孔を殆ど含まないが、固相変態させたアナターゼでも酸素欠陥由来の2eV付近のピークは観察されていないことから酸素空孔が少ないことが示唆される。(関崎君2018.3修了)

Ref.

S. Sekizaki, M. Osada, and K. Nagashio, "Molecularly-thin Anatase field-effect transistors fabricated through the solid state transformation of titania nanosheets", Nanoscale, 2017, 9, 6471–6477.